Учебная работа. Учебное пособие: Синтез схемы шифратора и кодопреобразователя для управления 1-разрядным 7-сегментным индикатором

РОССИЙСКИЙ ХИМИКО-ТЕХНОЛОГИЧЕСКИЙ УНИВЕРСИТЕТ

ИМ.Д.И. МЕНДЕЛЕЕВА

НОВОМОСКОВСКИЙ ИНСТИТУТ

синтез схемы шифратора и кодопреобразователя для управления 1-разрядным 7-сегментным индикатором

Методические указания

Под редакцией В.И. Воробьева

Новомосковск 2001

УДК 681.322

ББК 32.973

С 387

Рецензенты:

Кандитат технических наук, доцент кафедры «Автоматизация производственных действий», НИ РХТУ им. Д.И. Менделеева, В.И. Иванков

Кандитат технических наук, доцент кафедры «Автоматизация производственных действий», НИ РХТУ им. Д.И. Менделеева, В.З. Магергут

Составитель: Прохоров В.С.

С 387 синтез схемы шифратора и кодопреобразователя для управления 1-разрядным 7-сегментным индикатором:

Методические указания / Под редакцией В.И. Воробьева.;

РХТУ им. Д.И. Менделеева, Новомосковский ин-т; Сост.:

В.С. Прохоров. — Новомосковск, 2001. — 28с.

В предлагаемом пособии даны описания и методические указания для выполнения личного задания по курсу «Схематехника», которые посодействуют студентам ознакомиться с синтезом комбинационной схемы управления семисегментным индикатором.

Ил.7. Табл.7. Библиогр: 5 назв.

УДК 681.322

ББК 32.973

Содержание

Введение- 4

1. порядок синтеза схемы шифратора и кодопреобразователя для управления 1-разрядным 7-сегментным индикатором- 5

2. Личное задание- 11

приложение 1- 15

Приложение 2- 22

Библиографический список- 26

Введение

Логические элементы – главный “строительный материал” цифровых систем обработки инфы и управления.

Логические элементы делают простые логические операции (конъюнкцию, дизъюнкцию, инверсию) над входной информацией, представленной в двоичной форме. Но реализация случайного вычислительного процесса, содержащего арифметические операции (сложение, вычитание, умножение) либо логические процедуры (поиск, сортировка, сопоставление, сдвиг и др.), также осуществляются схемами, состоящими из логических частей. Таковым образом, логические элементы образуют всепригодную среду, обеспечивающую арифметическую и логическую обработку входной двоичной инфы.

Работа с логическими элементами просит не только лишь знакомства с их принципными схемами и техническими чертами, да и познания главных положений алгебры логики, теории переключательных схем, также умения по определенным правилам синтезировать логические схемы с данными чертами. Выполнение предлагаемого задания дозволит приобрести главные нужные для инженера способности.

1. порядок синтеза схемы шифратора и кодопреобразователя для управления 1-разрядным 7-сегментным индикатором

Проиллюстрируем методику решения задачки на примере.

1. Входные данные вводятся в унитарном коде. Унитарный код двоичного n-разрядного числа представляется 2n разрядами, лишь один из которых равен 1. Для преобразования этого кода в двоичный код следует применить шифратор. Шифратор должен иметь 10 входов, любому из которых соответствует одно из чисел 0, 1, 2,…,9. Число 9 в двоичном коде представляется разрядами: 1001, т.е. шифратор должен иметь четыре выхода. В согласовании с этими требованиями составляют таблицу истинности (табл.1).

Таблица 1

Таблица истинности шифратора

№

Входные

переменные

Выходные переменные

пп

x0

x1

x2

x3

x4

x5

x6

x7

x8

x9

y1

y2

y3

y4

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

0

0

0

0

0

0

0

1

2

0

0

1

0

0

0

0

0

0

0

0

0

1

0

3

0

0

0

1

0

0

0

0

0

0

0

0

1

1

4

0

0

0

0

1

0

0

0

0

0

0

1

0

0

5

0

0

0

0

0

1

0

0

0

0

0

1

0

1

6

0

0

0

0

0

0

1

0

0

0

0

1

1

0

7

0

0

0

0

0

0

0

1

0

0

0

1

1

1

8

0

0

0

0

0

0

0

0

1

0

1

0

0

0

9

0

0

0

0

0

0

0

0

0

1

1

0

0

1

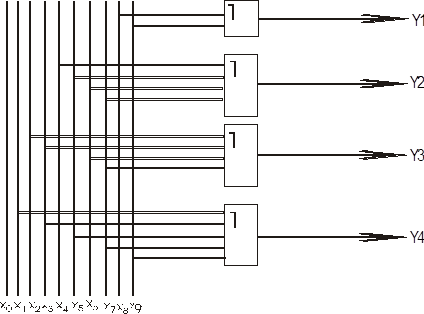

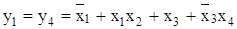

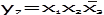

2. Получают логическую функцию шифратора в виде СДНФ методом записи “по единицам” (табл.1):

y1=x8+x9;

y2=x4+x5+x6+x7;

y3=x2+x3+x6+x7;

y4=x1+x3+x5+x7+x9

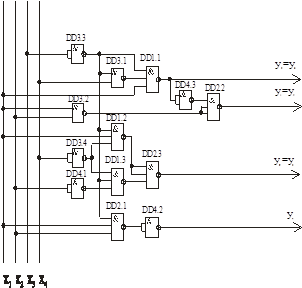

3. Используя приобретенные уравнения можно синтезировать многофункциональную схему шифратора в логическом базисе И, ИЛИ, НЕ (рис.1):

Рис.1. Многофункциональная схема шифратора на логических элементах либо для синтеза шифратора в логических базисах И-НЕ либо ИЛИ-НЕ следует применить закондвойной инверсии и закон инверсии (закон Де Моргана):

Опосля выбора из табл.4 микросхем синтезируют принципную электронную схему шифратора в данном табл.5 базисе.

4. Допустим, что крайние четыре числа номера зачетной книги образуют число 3011, т.е. должны индицироваться лишь стилизованные числа 0, 1, 3, а при вводе других цифр — знак

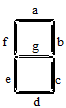

5. При составлении таблицы истинности кодопреобразователя (табл.2) учитывают, что входные данные вводятся в двоичном коде, а наличие высочайшего потенциала на выходах кодопреобразователя y1, y2, y3,…, y7 вызывает свечение соответственно сектора a, b, c, d, e, f, g 7-сегментного индикатора.

Таблица 2

Таблица истинности кодопреобразователя

№

Входные

Выходные переменные

пп

переменные

a

b

c

d

e

f

g

x4

x3

x2

x1

y1

y2

y3

y4

y5

y6

y7

0

0

0

0

0

1

1

1

1

1

1

0

1

0

0

0

1

0

1

1

0

0

0

0

2

0

0

1

0

1

0

0

1

1

1

0

3

0

0

1

1

1

1

1

1

0

0

1

4

0

1

0

0

1

0

0

1

1

1

0

5

0

1

0

1

1

0

0

1

1

1

0

6

0

1

1

0

1

0

0

1

1

1

0

7

0

1

1

1

1

0

0

1

1

1

0

8

1

0

0

0

1

0

0

1

1

1

0

9

1

0

0

1

1

0

0

1

1

1

0

10. .15

х

х

х

х

х

х

х

Эмблемой “х” в табл. 2 обозначены безразличные состояния выходных переменных.

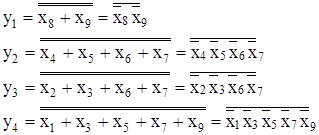

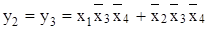

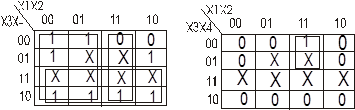

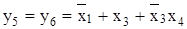

6. Для нахождения МДНФ используют диаграммы Вейча-Карно (рис.2). Из табл.2 видно, что y1=y4; y2=y3; y5=y6.

Рис.2. Диаграммы Вейча-Карно для кодопреобразователя

На диаграммах Вейча-Карно безразличные состояния входных переменных, отмеченные эмблемой “х” и включенные в контуры, числятся единичными, а вне контуров – нулевыми.

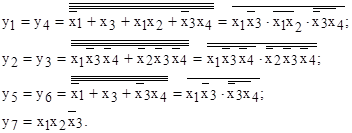

7. Для реализации многофункциональной схемы в базисе И-НЕ конвертируют приобретенные МДНФ, применяя законы двойной инверсии и инверсии (закон Де Моргана):

8. Для реализации многофункциональной схемы в базисе ИЛИ-НЕ конвертируют приобретенные МДНФ, применив обозначенные законы:

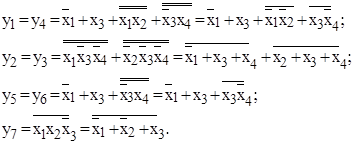

9. Схема кодопреобразователя в логическом базисе И, ИЛИ, НЕ (рис.3):

Рис.3. Многофункциональная схема кодопреобразователя в логическом базисе И, ИЛИ, НЕ

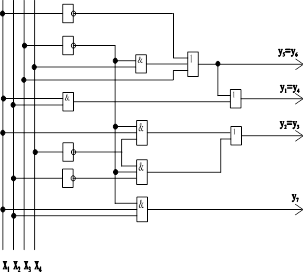

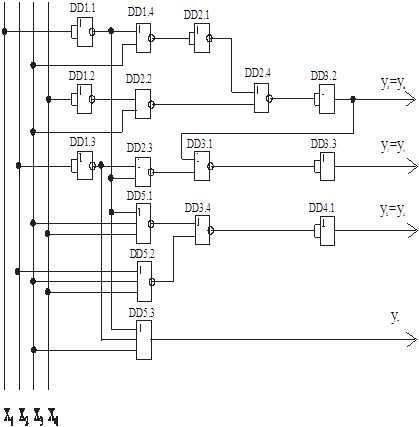

10. Схема кодопреобразователя в логическом базисе И-НЕ на логических элементах типа К176ЛА7 и К176ЛА9 (рис.4):

DD1, DD2: K176ЛА9 — 3х3 И-НЕ

DD3, DD4: K176ЛА7 — 4х2 И-НЕ

Рис.4. Принципная электронная схема кодопреобразователя в логическом базисе И-НЕ

11. Потому что меж входом x3 и выходом y1 включено 5 логических частей, то задержка кодопреобразователя равна

tз=5 tз. ср=5(200…300) =(1000…1500) нс.

12. Схема кодопреобразователя в логическом базисе ИЛИ-НЕ на логических элементах типа К176ЛЕ5 и К176ЛЕ10 (рис.5):

DD1 – DD4: K176ЛЕ5 — 4х2 ИЛИ-НЕ

DD5: K176ЛЕ10 — 3х3 ИЛИ-НЕ

Рис.5. Принципная электронная схема кодопреобразователя в логическом базисе ИЛИ-НЕ

13. Потому что меж входом x1 и выходом y1 включено 7 логических частей, то задержка кодопреобразователя равна

tз=7(200…300) =(1400…2100) нс.

2. Личное задание

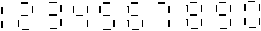

Синтезировать схему шифратора и кодопреобразователя, который управляет работой одноразрядного семисегментного индикатора. При всем этом должны индицироваться стилизованные числа (Рис.6):

Рис.6. Стилизованные числа 7-сегментного индикатора

Эти стилизованные числа должны совпадать с 4-мя крайними цифрами номера студенческого билета (зачетной книги).

При поступлении на вход кодопреобразователя остальных цифровых данных должен высвечиваться спецсимвол, избранный из табл.3.

Таблица 3

Спецсимвол

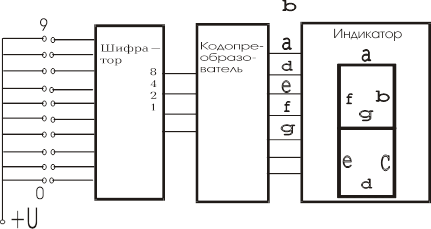

Входные данные в кодопреобразователь вводятся двоичным кодом, который получают из унитарного кода при помощи шифратора (рис.7).

Рис.7. Структурная схема шифратора и кодопреобразователя для управления 1-разрядным 7-сегментным индикатором

Согласно варианту нужно:

1. Составить таблицу истинности для шифратора.

2. Отыскать СДНФ шифратора.

3. Избрать из табл.4 либо табл. П2.2 пригодные ИМС и создать на их базе принципную электронную схему шифра в данном базисе (табл.5).

Таблица 4

Рекомендуемый список микросхем

Условное обозначение ИМС

Состав и функциональное предназначение ИМС

Тип логики

К155ЛА1

2х4 И-НЕ

ТТЛ

К155ЛА3

4х2 И-НЕ

ТТЛ

К155ЛА4

3х3 И-НЕ

ТТЛ

К155ЛЕ1

4х2 ИЛИ-НЕ

ТТЛ

К176ЛЕ10

3х3 ИЛИ-НЕ

КМОП

К176ЛЕ6

2х4 ИЛИ-НЕ

КМОП

К176ЛЕ5

4х2 ИЛИ-НЕ

КМОП

К176ЛА7

4х2 И-НЕ

КМОП

К176ЛА8

2х4 И-НЕ

КМОП

К176ЛА9

3х3 И-НЕ

КМОП

К500ЛМ102

4х2 ИЛИ-НЕ

ЭСЛ

К500ЛМ106

3х3 ИЛИ-НЕ

ЭСЛ

К500ЛМ109

4 ИЛИ-НЕ, 5 ИЛИ-НЕ

ЭСЛ

К561ЛЕ5

4х2 ИЛИ-НЕ

КМДП

К561ЛЕ6

2х4 ИЛИ-НЕ

КМДП

К561ЛА7

4х2 И-НЕ

КМДП

К561ЛА8

2х4 И-НЕ

КМДП

К561ЛА9

3х3 И-НЕ

КМДП

К561ЛА10

3х3 ИЛИ-НЕ

КМДП

К555ЛА3

4х2 И-НЕ

ТТЛШ

К555ЛЕ1

4х2 ИЛИ-НЕ

ТТЛШ

К555ЛН1

6 НЕ

ТТЛШ

К555ЛИ1

4х2 И

ТТЛШ

К555ЛИ3

3х3 И

ТТЛШ

К555ЛА4

3х3 И-НЕ

ТТЛШ

К555ЛА1

2х4 И-НЕ

ТТЛШ

К555ЛЕ4

3х3 ИЛИ-НЕ

ТТЛШ

К531ЛА3П

4х2 И-НЕ

ТТЛШ

К531ЛЕ1П

4х2 ИЛИ-НЕ

ТТЛШ

К531ЛН1П

6 НЕ

ТТЛШ

К531ЛИ3П

3х3 И

ТТЛШ

К531ЛА1П

2х4 И-НЕ

ТТЛШ

К531ЛА2П

8 И-НЕ

ТТЛШ

Запись 2х4 И-НЕ значит, что в одном корпусе ИМС находятся два 4-входовых логических элемента И-НЕ. Наиболее подробная информация о микросхемах ТЛЛ представлена в прил.2.

Таблица 5

Базис для синтеза шифратора

Крайняя цифра номера зачетной книги

Четная

Нечетная

Базис

ИЛИ-НЕ

И-НЕ

4. Найти время задержки для синтезированной схемы шифратора, используя данные табл.6 либо табл. П2.1

Таблица 6

время задержки

Серия ИМС

Время задержки,

нс

К155

20

К531

5

К555

10

К561

50

К500

2

К176

200

5. Составить таблицу истинности для кодопреобразователя.

6. При помощи диаграмм Вейча-Карно отыскать МДНФ для выходных переменных кодопреобразователя.

7. Избрать из табл.4 либо табл. П2.2 пригодные ИМС и создать на их базе принципную электронную схему кодопреобразователя в данном в табл.7 базисе.

Таблица 7

Базис для синтеза кодопреобразователя

Предпоследняя цифра номера зачетной книги

Четная

Нечетная

Базис

ИЛИ-НЕ

И-НЕ

8. Найти время задержки для синтезированной схемы кодопреобразователя.

9. Начертить полную принципную электронную схему устройства. Принципную электронную схему выполнить в согласовании ГОСТ 2.743-82 “Обозначения условные графические в схемах. Элементы цифровой техники”. Можно применять советы Приложения 1.

Приложение 1

Двоичные логические элементы

Общие принципы построения условных графических обозначений, также условные графические обозначения двоичных логических частей, выпускаемых индустрией в виде цифровых микросхем, установлены ГОСТ 2.743-82.

Условное графические обозначение двоичного логического элемента имеет форму прямоугольника, который может содержать три поля: основное и два доп. В главном поле помещают информацию о функции, выполняемой логическим элементом — знак функции и по мере необходимости доп данные по ГОСТ 2.304-68. В доп полях помещают условные обозначения входов и выходов, именуемые метками. Доп поля и метки обычно имеют комбинационные и сложные логические элементы, у каких все входы (выходы) логически неравноценны. (См. табл. П.1.1, табл. П.1.2, табл. П.1.3, табл. П.1.4)

Все размеры условного графического обозначения по высоте должны быть кратны неизменной величине С. При всем этом расстояние меж горизонтальной стороной прямоугольника и наиблежайшей входной (выходной) линией, также меж примыкающими входными (выходными) линиями обязано быть не наименее величины С. При ручном (неавтоматизированном) выполнении графического обозначения С³5 мм.

Таблица П.1.1

Знаки логических операций

Наименование

Обозна-чение

Наименование

Обозна-чение

ИЛИ

1

Регистр

RG

Монтажное ИЛИ

1

Шифратор

CD

И

&

Дешифратор

DC

Монтажное И

&

Кодовый преобразователь

X/Y

Триггер

T

Сумматор

SM

Триггер двухступенчатый

TT

Пороговый элемент

Продолжение табл. П.1.1

генератор

Г

Усилитель

Одновибратор

S

Формирователь сигнала

F

Счетчик:

а) двоичный

СТ2

Задержка временная

б) десятичный

СТ10

Таблица П.1.2

Начертание условных обозначений цифровых микросхем

Наименование

Обозначение

Вход для раздельной установки триггера в состояние “1” (S-вход)

S

Вход для раздельной установки триггера в состояние “0” (R-вход)

R

Вход для установки состояния “1” в всепригодном JK-триггере (J-вход)

J

Вход для установки состояния “0” в всепригодном JK-триггере (К-вход)

K

Счетный вход (Т-вход)

T

Информационный вход для установки триггера в состояние “1” и “0” (D-вход)

D

Предварительный управляющий вход для разрешения приема инфы (V-вход)

V *

Исполнительный управляющий вход для воплощения приема инфы. Вход синхронизации (С-вход)

C*

1. Метки V и С используют в комбинационных логических элементах для обозначения входов, подготавливающих и разрешающих выполнение логической операции.

2. По мере необходимости к буковкам добавляют числа, к примеру

S1, S2, C1, C2 и т.д.3. Метки S, R, J, K, T, D, V и С —

исходные буковкы британских слов.

Таблица П.1.3

Примеры условных обозначений логических частей

Наименование

Обозначение

Основное поле. Малые размеры, мм:

a: 10 — 12

b: 8 — 12

При помещении доп данных:

a: 20 — 25

b: 12 — 17

Основное поле с левым доп полем, c ³ 5 мм

Основное поле с правым доп полем, c ³ 5 мм

Продолжение табл. П.1.3

Входы логического элемента

Выходы логического элемента

Прямой статический вход (фрагмент условного обозначения)

Прямой статический выход

Продолжение табл. П.1.3

Инверсный статический вход

Инверсный статический выход

Прямой динамический вход

Прямой динамический выход

Продолжение табл. П.1.3

Инверсный динамический вход

Инверсный динамический выход

Вывод, не несущий логической инфы

* Допускается ориентация условного графического обозначения, при котором входы размещаются сверху, а выходы — снизу.

Таблица П.1.4

Примеры условных обозначений многофункциональных частей

Наименование

Обозначение

Наименование

Обозначение

Повтори-

тель

JK-триггер асинхронный

НЕ (инвертор)

Т-триггер (триггер со счетным входом)

ИЛИ (дизъюнк

тор)

D-триггер со статиче

ским управле

нием

ИЛИ-НЕ (элемент Приса)

Цифровой элемент задержки

И (конъюнк

тор)

Одновибратор с импульсным входом

Продолжение табл. П.1.4

И-НЕ (элемент Шеффера)

Пороговый элемент (триггер Шмитта)

RS-триггер асинхрон

ный

Регистр с реверсив

ным

сдвигом 4-разрядный

генератор

Счетчик двоично-десятич-

ный 4-разряд-

ный

Дешифратор на 4 разряда для газоразрядных индикаторов

приложение 2

Сведения о микросхемах ТТЛ серий 133, 134, 155 и 531

Таблица П.2.1

электронные характеристики базисных схем ТТЛ-типа

Серия

Параметр

133, 155

134

531 с диодиками

Шотки

Выходное напряжение “0”

, В, не наиболее

, В, не наиболее

Выходное напряжение “1”

, В, не наименее

, В, не наименее

Коэффициент разветвления

по выходу

Среднее время задержки  , нс, не наиболее

, нс, не наиболее

Средняя статистическая мощность употребления, РПОТ, мВт, не наиболее

Частота переключений f, Мгц, не наиболее

0,4

2,4

10

20

(СН=15 пФ)

22

10

0,3

2,3

10

100

(СН=40 пФ)

2

3

0,5

2,7

10

5

(СН=15 пФ)

19

50

Таблица П.2.2

Функциональное предназначение ИС ТТЛ

Функциональное предназначение

Обозначение

Номер

рисунка

Четыре логических элемента 2И-НЕ (133,155)

ЛА3

П.1.1, а

Четыре логических элемента 2И-НЕ (134)

ЛБ1

П.1., б

Три логических элемента 3И-НЕ (133, 155)

ЛА4

П.1.2

Два логических элемента 4И-НЕ (133, 155)

ЛА1

П.1.3

(для 155)

Продолжение табл. П.2.1

Два логических элемента 4И-НЕ (134)

ЛБ2

-

Логический элемент 8И-НЕ (133, 134, 155)

ЛА2

П.1.4

Два логических элемента 2И-2ИЛИ-НЕ (133, 134, 155)

ЛР1

П.1.5

Триггер Шмитта с логическим элементом на 6 логических частей НЕ (155)

ЛН1

П.1.6

Четыре логических элемента 2ИЛИ-НЕ (133, 155)

ЛЕ1

П.1.7

Четыре логических элемента 2И (133, 155)

ЛИ1

П.1.8

Два логических элемента 4И (155)

ЛИ6

-

Четыре логических элемента 2ИЛИ (133, 155)

ЛЛ1

П.1.9

Два триггера Шмитта с логическим элементом на входе (133, 155)

ТЛ1

П.1.10

Четыре D-триггера с прямым и инверсным выходами (133, 155)

ТМ7

П.1.11

Четыре D-триггера (133, 155)

ТМ5

П.1.12

Два D-триггера (133, 134, 155)

ТМ2

П.1.13

JK-триггер с логикой на входе (133, 134, 155)

ТВ1

П.1.14 (133,155)

Два JK-триггера (134)

ТВ — комплекс устройств для передачи движущегося изображения и звука на расстояние)14

-

Четыре 2-входовых элемента “исключающее ИЛИ” (155)

ЛП5

-

Селектор-мультиплексор на восемь каналов со стробированием (133, 155)

ЛП7

П.1.15

Дешифратор-демультиплексор четыре полосы на 16 (133, 134, 155)

ИД3

П.1.16

Два 4-входовых расширителя по ИЛИ (133, 155)

ЛД1

-

Одноразрядный полный сумматор (133, 155)

ИМ1

-

Двухразрядный сумматор (133, 155)

ИМ2

-

Четырехразрядный сумматор (133, 155)

ИМ3

-

Одновибратор с логическим элементом на входе (133, 155)

АГ1

-

Четырехразрядный всепригодный сдвигающий регистр (133, 134, 155)

ИР1

П.1.17 (133,155)

Реверсивный 8-разрядный регистр сдвига (133, 155)

ИР13

-

Восьмиразрядная схема контроля четности и нечетности (134, 155)

ИП2

-

Продолжение табл. П.2.1

Схема резвого переноса для арифметическо-логического узла (134, 155)

ИП4

-

Четырехразрядный двоичный реверсивный счетчик (133, 155)

ИЕ7

П.1.18

Двоичный счетчик (133, 134, 155)

ИЕП5

П.1. 19 (133,155)

Двухразрядный сумматор (133, 155)

ИМ2

-

Четырехразрядный сумматор (133, 155)

ИМ3

-

Одновибратор с логическим элементом на входе (133, 155)

АГ1

-

Библиографический перечень

1. Калабеков Б.А., Мамзелев И.А. Цифровые устройства и микропроцессорные системы. – М.: Радио и связь, 1987. – 400 с.

2. Применение интегральных микросхем в ЭВТ / Данилов Р.В., Ельцова С.А., Иванов Ю.П. и др. – М.: Справочник. Радио и связь, 1987. – 384 с.

3. Проектирование импульсных и цифровых устройств радиотехнических систем: Учебное пособие / Под ред. Ю.М. Казаринова. – М.: Высшая школа, 1985. – 319 с.

4. Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. – Л.: Электроатомиздат, 1986. – 280 с.

5. Аналоговые и цифровые интегральные микросхемы: Справочное пособие / Под ред. С.В. Якубовского. – М.: Радио и связь, 1984. – 432 с.

]]>