Учебная работа. Курсовая работа: Розробка ВІС в базисі БМК 1515ХМ1 пристрою множення який множить 3-розрядне число на 2-розрядне

Вінницький національний технічний університет

Інститут інформаційних технологій і компьютер’ютерної інженерії

Кафедра ПЗ

Пояснювальна записка

до курсової роботи з дисципліни

“САПР засобів обчислювальної техніки”

Розробка ВІС в базисі БМК 1515ХМ1пристрою множення, який множить3-розрядне число на 2-розрядне

Розробив студент

Кравець В.В.

Вінниця ВНТУ 2009

Анотація

В курсовій роботі розроблена велика інтегральна схема пристрою множення, який умножать 3-розрядне число на 2-розрядне, в базисі БМК 1515ХМ1.

Проведений багатоваріантний аналіз розв’язків поставленої задачі, розроблено принципову електричну схему, логічну модель і тест перевірки. Також розраховано швидкодію та визначено необхідну кількість базових комірок. Розробка схеми електричної принципової, її моделювання та тестування проведено з використанням пакету прикладних програм OrCAD 9.1.

Схеми пристрою, автоматичне трасування та трафаретні креслення з’єднань наведені у додатках.

Індивідуальне завдання

на курсову боту з дисципліни ”Системи автоматизованого проектування засобів обчислювальної техніки”

Розробити в базисі БМК 1515ХМ1 велику інтегральну схему пристрою множення, який умножать 3-розрядне число на 2-розрядне.Провести багатоваріантний аналіз розв’язку поставленої задачі, розробити електричну принципову схему, логічну модель, тест перевірки, розрахувати швидкодію, визначити кількість базових комірок, виконати трасування.

– кількість базових комірок – не більше 50;

– затримка операції – не більше 100 нс.

Трасування виконати в автоматичному та ручному режимах.

Затверджено на засіданні кафедри ПЗ, протокол № 2 від 18 вересня

Зміст

ВСТУП

1. БАГАТОВАРІАНТНИЙ АНАЛІЗ ВИРІШЕННЯ ОСНОВНОЇ ЗАДАЧІ

2. РОЗРОБКА СХЕМИ ЕЛЕКТРИЧНОЇ ПРИНЦИПОВОЇ

3. РОЗРАХУНОК ШВИДКОДІЇ ПРИСТРОЮ

4. РОЗРОБКА ЛОГІЧНОЇ МОДЕЛІ

5. РОЗРОБКА ТЕСТУ ПЕРЕВІРКИ ТА ЛОГІЧНЕ МОДЕЛЮВАННЯ

6. РОЗРАХУНОК АПАРАТНИХ ВИТРАТ

7. РОЗРОБКА ТРАФАРЕТУ ТРАСУВАННЯ

ВИСНОВКИ

СПИСОК ВИКОРИСТАНОЇ ЛІТЕРАТУРИ

Додаток А. ТЕХНІЧНЕ ЗАВДАННЯ

Додаток Б. СХЕМА ЕЛЕКТРИЧНА ПРИНЦИПОВА

Додаток В. ТРАФАРЕТ АВТОМАТИЧНОГО ТРАСУВАННЯ

Додаток Г. ТРАФАРЕТ РучнОГО трасування

Вступ

Основним засобом зниження вартості проектування і, головне, прискорення темпів розробки нових видів мікроелектронної апаратури є системи автоматизованого проектування (САПР). Для часткової уніфікації топології інтегральних схем (ІС) використовувалось проектування схем на основі набору типових комірок.

Базовий матричний кристал (БМК) – велика інтегральна схема, яка на відміну від ПЛІС програмується технологічно, шляхом нанесення маски з’єднань останнього шару металізації. БМК з маскою замовника звичайно виготовлялися під замовлення невеликими серіями. Вказані елементи розташовуються на кристалі матричним методом (в кутах прямокутної решітки). Тому такі схеми нередко називають матричними ВІС. Як і в схемах на типових комірках топологія набору логічних елементів розробляється завчасно. Однак у даному випадку топологія логічного елемента створюється на основі часто розташованих найпростіших елементів[1].

Бібліотека логічних елементів розроблена на основі компонентів базової комірки. Бібліотечний елемент реалізується за допомогою тої чи іншої топологічної конфігурації в змінному шарі. Топологія дерматологического елемента БМК совершенно точно визначає його функціональний зміст[2].

Структурно БМК є матрицею, яка складається з 22 стовпців і 46 рядків комірок типу VW, між якими перебувають полікремнієві шини комутації. По периметру кристалу розміщені елементи входу-виходу з контактними площадками. Метою даного курсового проекту є отримання навичок розробки принципових схем за допомогою різних методів, проведення трасування і тестування роботи пристрою.

1

.

Багатоваріантний аналіз вирішення основної задачі

Поставлену задачку можна вирішити різними методами:

– розробити схему комбінаційного типу;

– використати матриці множення;

– скласти структурній пристрій множення на базі суматора.

Якщо використовувати матриці множення, то потрібно організувати відповідні умови даної задачі. При цьому буде істотна апаратна надлишковість, а відповідно високі апаратні затрати, проте можна досягти високої швидкодії.

Якщо складати пристрій на базі суматора, то необхідно організовувати складну структуру з керуючим автоматом. В цьому випадку матимемо не тільки високі апаратні витрати, а й невисоку швидкодію. Також нераціональним є розробка керуючого автомату для такої нескладної задачі[3].

Схема комбінаційного типу в даному випадку має ряд переваг:

– простота та прозорість реалізації;

– висока швидкодія пристрою;

– мінімальні апаратні затрати;

– мінімальна можливість збою при правильній реалізації.

Отже, найдоцільнішим варіантом вирішення поставленої задачі є розробка комбінаційного пристрою.

2. Розробка схеми електричної принципової

Оскільки вибрано комбінаційний спосіб побудови пристрою множення, постає задачка побудови таблиці істинності пристрою(табл. 2.1). 2-розрядне число позначене А, а 3-розрядне В. Відповідно вихідна сукупність сигналів – С. Числа, записані після букви позначення, означають порядок розряду.

Таблиця 2.1 – Таблиця істинності

Вхідні сигнали

Вихідні сигнали

А2

А1

В4

В2

В1

С16

С8

С4

С2

С1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

1

1

1

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

1

0

0

1

0

0

0

0

1

0

1

0

1

0

0

0

0

1

0

0

1

0

1

1

0

0

0

1

1

0

1

1

0

0

0

0

1

0

0

0

1

1

0

1

0

0

1

0

1

0

1

1

1

0

0

0

1

1

0

0

1

1

1

1

0

0

1

1

1

1

0

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

1

0

1

0

0

1

0

0

0

1

0

0

1

0

0

1

1

0

0

1

1

0

1

0

1

0

0

0

1

0

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

0

0

1

1

0

0

1

0

1

1

1

0

1

1

1

0

1

1

0

0

0

0

0

0

0

0

1

1

0

0

1

0

0

0

1

1

1

1

0

1

0

0

0

1

1

0

1

1

0

1

1

0

1

0

0

1

1

1

1

0

0

0

1

1

0

0

1

1

1

0

1

0

1

1

1

1

1

1

1

1

0

1

0

0

1

0

1

1

1

1

1

1

0

1

0

1

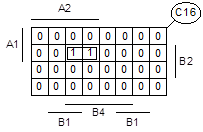

Наступною задачею в побудові схеми є мінімізація функцій розрядів вихідної змінної. Мінімізація проводиться згідно з табл. 2.1 за допомогою діаграм Вейча(рис. 2.1 – 2.5).

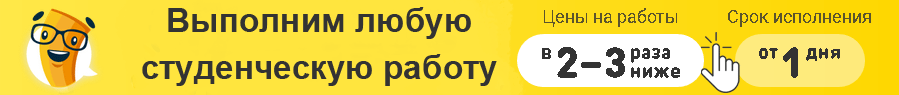

Набросок 2.1 – Діаграма Вейча для функції С1

Набросок 2.2 – Діаграма Вейча для функції С2

Набросок 2.3 – Діаграма Вейча для функції С4

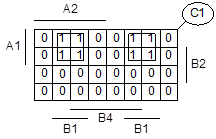

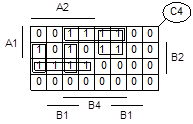

Набросок 2.4 – Діаграма Вейча для функції С8

Набросок 2.5 – Діаграма Вейча для функції С16

Відповідно до побудованих діаграм Вейча для функцій С записується їх аналітичний вигляд і приводяться до базису БМК.

;

;

;

;

;

;

;

;

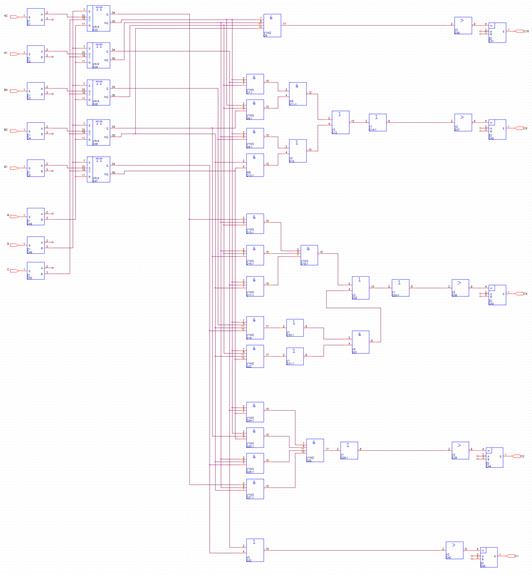

Результуюча схема утворюється при реалізації даних функцій в базисі БМК1515. Схема електрична принципова наведена в додатках(Додаток Б)

3. Розрахунок швидкодії пристрою

Проектуючи принципові електричні схеми, слід приблизно оцінити середній сумарний час затримки на ланцюжку логічних елементів, не враховуючи паразитних ємностей.

Середній сумарний час затримки обчислюється за формулою:

Тсер

= Т1

+ Т2

+ … + Тn

,

де Ті

– середній час затримки поширення сигналу на і-му елементі.

Через розкид технологічних параметрів середній час затримки поширення сигналу може відрізнятися від обчислених даних, тому треба мати припас за цим параметром[4].

Розглянемо найдовші шлях в схемі:

T1

=  Z1

Z1

+  V4V4

V4V4

+  V1W2

V1W2

+ + V2

V2

+ Z2

Z2

= 14,3 + 24,4 + 20 + 3,3 + 14,3 = 76,3(нс)

T2

=  Z1

Z1

+  V4V4

V4V4

+  V1W3

V1W3

+  W

W

8

+  V3

V3

+ V1

V1

+ V2

V2

+ Z2

Z2

= 14,3 + 24,4 +12 + 6 + 6+3,8+3,3+14,3 = 84,1(нс)

T3

=  Z1

Z1

+  V4V4

V4V4

+  V1W2

V1W2

+  V1

V1

+  V4

V4

+ V3

V3

+ V1

V1

+ V2

V2

+ Z2

Z2

= 14,3 + 24,4 + 20 + 3,8 + 6+6+3,8+3,3+14,3 = 95,9(нс)

T4

=  Z1

Z1

+  V4V4

V4V4

+  V1W

V1W

3

+ V1W

V1W

2

+ V1

V1

+ V2

V2

+ Z2

Z2

= 14,3 + 24,4 +12 + 20 +3,8+3,3+14,3 = 92,1(нс)

T5

=  Z1

Z1

+  V

V

4

V

4

+  V3

V3

+ V2

V2

+ Z2

Z2

= 14,3 + 24,4 + 6+3,3+14,3 = 62,3(нс)

З розглянутих шляхів проходження сигналу найдовшим є Т3

. Отже, затримка розробленої схеми становить Т = 95,9(нс). Можна зробити висновок, що схема задовольняє поставлені вимоги.

4

.

Розробка логічної моделі

Логічне моделювання цифрового виробу полягає в розробці та послідовному налагодженні логічної моделі, яка є сукупністю проектної інформації про електричну схему і конструктивних виводів у обсязі, достатньому для проектування топології й автоматичного синтезу програм контролю. Опис електронної схеми зводиться до послідовного опису структур, що її покривають. При цьому кожний функціонально-закінчений фрагмент, який повторюється, подається окремою структурою і ідентифікується своїм ім’ям. Описуючи зв’язки, кожний вивід згадується тільки один раз. Поява імені будь-якого виводу ще один раз вважається помилкою.

Виконаємо логічне моделювання даного пристрою:

структура «Scheme»

compinst «D1»

(patternName «Z1»)

(compvalue «Z1»))

(compinst «D10»

(patternName «DIP.100B/18/W.300/L.1050»)

(compvalue «W8»))

(compinst «D11»

(patternName «DIP.100B/18/W.300/L.1050»)

(compvalue «W8»))

(compinst «D12»

(patternName «DIP.100B/10/W.300/L.650»)

(compvalue «V3»))

(compinst «D13»

(patternName «DIP.100B/10/W.300/L.650»)

(compvalue «V3»))

(compinst «D14»

(patternName «DIP.100B/10/W.300/L.650»)

(compvalue «V1»))

(compinst «D15»

(patternName «DIP.100B/28/W.300/L.1550»)

(compvalue «V1W3»))

(compinst «D16»

(patternName «DIP.100B/28/W.300/L.1550»)

(compvalue «V1W3»))

(compinst «D17»

(patternName «DIP.100B/28/W.300/L.1550»)

(compvalue «V1W3»))

(compinst «D18»

(patternName «DIP.100B/28/W.300/L.1550»)

(compvalue «V1W3»))

(compinst «D19»

(patternName «DIP.100B/28/W.300/L.1550»)

(compvalue «V1W2»))

(compinst «D2»

(patternName «Z1»)

(compvalue «Z1»))

(compinst «D20»

(patternName «DIP.100B/28/W.300/L.1550»)

(compvalue «V1W2»))

(compinst «D21»

(patternName «DIP.100B/10/W.300/L.650»)

(compvalue «V4»))

(compinst «D22»

(patternName «DIP.100B/10/W.300/L.650»)

(compvalue «V3»))

(compinst «D23»

(patternName «DIP.100B/10/W.300/L.650»)

(compvalue «V1»))

(compinst «D24»

(patternName «DIP.100B/28/W.300/L.1550»)

(compvalue «V1W3»))

(compinst «D25»

(patternName «DIP.100B/28/W.300/L.1550»)

(compvalue «V1W3»))

(compinst «D26»

(patternName «DIP.100B/28/W.300/L.1550»)

(compvalue «V1W3»))

(compinst «D27»

(patternName «DIP.100B/28/W.300/L.1550»)

(compvalue «V1W3»))

(compinst «D28»

(patternName «DIP.100B/28/W.300/L.1550»)

(compvalue «V1W2»))

(compinst «D29»

(patternName «DIP.100B/10/W.300/L.650»)

(compvalue «V1»))

(compinst «D3»

(patternName «Z1»)

(compvalue «Z1»))

(compinst «D30»

(patternName «DIP.100B/10/W.300/L.650»)

(compvalue «V1»))

(compinst «D31»

(patternName «DIP.100B/10/W.300/L.650»)

(compvalue «V1»))

(compinst «D32»

(patternName «DIP.100B/10/W.300/L.650»)

(compvalue «V3»))

(compinst «D33»

(patternName «DIP.100B/66/W.300/L.3450»)

(compvalue «V4V4»))

(compinst «D34»

(patternName «DIP.100B/66/W.300/L.3450»)

(compvalue «V4V4»))

(compinst «D35»

(patternName «DIP.100B/66/W.300/L.3450»)

(compvalue «V4V4»))

(compinst «D36»

(patternName «DIP.100B/10/W.300/L.650»)

(compvalue «V2»))

(compinst «D37»

(patternName «DIP.100B/10/W.300/L.650»)

(compvalue «V2»))

(compinst «D38»

(patternName «DIP.100B/10/W.300/L.650»)

(compvalue «V2»))

(compinst «D39»

(patternName «DIP.100B/10/W.300/L.650»)

(compvalue «V2»))

(compinst «D4»

(patternName «Z1»)

(compvalue «Z1»))

(compinst «D40»

(patternName «DIP.100B/10/W.300/L.650»)

(compvalue «V2»))

(compinst «D41»

(patternName «Z2»)

(compvalue «Z2»))

(compinst «D42»

(patternName «Z2»)

(compvalue «Z2»))

(compinst «D43»

(patternName «Z2»)

(compvalue «Z2»))

(compinst «D44»

(patternName «Z2»)

(compvalue «Z2»))

(compinst «D45»

(patternName «Z2»)

(compvalue «Z2»))

(compinst «D46»

(patternName «DIP.100B/66/W.300/L.3450»)

(compvalue «V4V4»))

(compinst «D47»

(patternName «DIP.100B/66/W.300/L.3450»)

(compvalue «V4V4»))

(compinst «D48»

(patternName «Z1»)

(compvalue «Z1»))

(compinst «D49»

(patternName «Z1»)

(compvalue «Z1»))

(compinst «D5»

(patternName «Z1»)

(compvalue «Z1»))

(compinst «D50»

(patternName «Z1»)

(compvalue «Z1»))

(compinst «D6»

(patternName «DIP.100B/28/W.300/L.1550»)

(compvalue «V1W2»))

(compinst «D7»

(patternName «DIP.100B/28/W.300/L.1550»)

(compvalue «V1W3»))

(compinst «D8»

(patternName «DIP.100B/28/W.300/L.1550»)

(compvalue «V1W3»))

(compinst «D9»

(patternName «DIP.100B/28/W.300/L.1550»)

(compvalue «V1W3»))

(net «N00151»

(node «D13» «10»)

(node «D14» «2»))

(net «N00173»

(node «D22» «10»)

(node «D23» «2»))

(net «B4»

(node «D3» «1»))

(net «B2»

(node «D4» «1»))

(net «A2»

(node «D1» «1»))

(net «A1»

(node «D2» «1»))

(net «N00224»

(node «D9» «15»)

(node «D12» «2»))

(net «N00337»

(node «D22» «4»)

(node «D21» «8»))

(net «N00269»

(node «D18» «7»)

(node «D17» «15»))

(net «N00293»

(node «D19» «17»)

(node «D30» «2»))

(net «N00281»

(node «D18» «15»)

(node «D22» «2»))

(net «N00236»

(node «D10» «12»)

(node «D12» «4»))

(net «N00176»

(node «D7» «15»)

(node «D11» «2»))

(net «N00263»

(node «D16» «15»)

(node «D18» «4»))

(net «N00200»

(node «D13» «2»)

(node «D11» «12»))

(net «N00212»

(node «D13» «4»)

(node «D12» «10»))

(net «N00248»

(node «D15» «15»)

(node «D18» «2»))

(net «N00520»

(node «D29» «6»)

(node «D39» «2»))

(net «C2»

(node «D44» «1»))

(net «C1»

(node «D45» «1»))

(net «N004870»

(node «D39» «8»)

(node «D44» «4»))

(net «N004900»

(node «D40» «8»)

(node «D45» «4»))

(net «N00508»

(node «D6» «17»)

(node «D36» «2»))

(net «N00512»

(node «D14» «6»)

(node «D37» «2»))

(net «N00516»

(node «D23» «6»)

(node «D38» «2»))

(net «N004780»

(node «D41» «4»)

(node «D36» «8»))

(net «N004810»

(node «D37» «8»)

(node «D42» «4»))

(net «C4»

(node «D43» «1»))

(net «N00122»

(node «D25» «7»)

(node «D24» «7»)

(node «D47» «38»)

(node «D10» «4»)

(node «D20» «13»))

(net «N00092»

(node «D9» «4»)

(node «D6» «9»)

(node «D15» «4»)

(node «D27» «4»)

(node «D26» «2»)

(node «D16» «2»)

(node «D34» «38»))

(net «N00590»

(node «D34» «34»)

(node «D7» «4»)

(node «D24» «4»)

(node «D32» «2»)

(node «D17» «4»))

(net «N00650»

(node «D46» «34»)

(node «D25» «4»)

(node «D16» «7»)

(node «D8» «7»))

(net «N00079»

(node «D25» «2»)

(node «D20» «7»)

(node «D24» «2»)

(node «D19» «7»)

(node «D17» «2»)

(node «D9» «2»)

(node «D7» «2»)

(node «D6» «7»)

(node «D8» «2»)

(node «D33» «38»))

(net «N00732»

(node «D9» «7»)

(node «D19» «9»)

(node «D35» «34»))

(net «N00107»

(node «D6» «11»)

(node «D35» «38»)

(node «D7» «7»)

(node «D8» «4»)

(node «D15» «7»)

(node «D16» «4»)

(node «D20» «9»))

(net «B1»

(node «D5» «1»))

(net «N00188»

(node «D11» «4»)

(node «D8» «15»))

(net «C8»

(node «D42» «1»))

(net «C16»

(node «D41» «1»))

(net «N00125»

(node «D46» «38»)

(node «D26» «4»)

(node «D6» «13»)

(node «D10» «2»)

(node «D19» «11»)

(node «D17» «7»)

(node «D20» «11»)

(node «D27» «7»))

(net «N02330»

(node «D32» «10»)

(node «D40» «2»))

(net «N00844»

(node «D33» «34»)

(node «D27» «2»)

(node «D15» «2»))

(net «N02935»

(node «D43» «4»)

(node «D38» «8»))

(net «N03117»

(node «D21» «4»)

(node «D31» «6»))

(net «N03105»

(node «D21» «2»)

(node «D30» «6»))

(net «N00332»

(node «D31» «2»)

(node «D20» «17»))

(net «N01078»

(node «D47» «34»)

(node «D19» «13»)

(node «D26» «7»)

(node «D32» «4»))

(net «N04471»

(node «D28» «11»)

(node «D26» «15»))

(net «N04441»

(node «D28» «7»)

(node «D24» «15»))

(net «N04486»

(node «D28» «13»)

(node «D27» «15»))

(net «N04453»

(node «D25» «15»)

(node «D28» «9»))

(net «N044074»

(node «D29» «2»)

(node «D28» «17»))

(net «N05876»

(node «D4» «2»)

(node «D46» «33»))

(net «N05837»

(node «D33» «33»)

(node «D1» «2»))

(net «N05852»

(node «D2» «2»)

(node «D34» «33»))

(net «N05864»

(node «D3» «2»)

(node «D35» «33»))

(net «N06267»

(node «D50» «3»)

(node «D47» «18»)

(node «D34» «18»)

(node «D35» «18»)

(node «D33» «18»)

(node «D46» «18»))

(net «R»

(node «D48» «1»))

(net «S»

(node «D49» «1»))

(net «C»

(node «D50» «1»))

(net «N05933»

(node «D5» «2»)

(node «D47» «33»))

(net «N06091»

(node «D33» «11»)

(node «D34» «11»)

(node «D46» «11»)

(node «D47» «11»)

(node «D35» «11»)

(node «D48» «3»))

(net «N06179»

(node «D35» «7»)

(node «D33» «7»)

(node «D34» «7»)

(node «D46» «7»)

(node «D47» «7»)

(node «D49» «3»))

5.

Розробка тесту перевірки та логічне моделювання

Для того щоб цілком перевірити розроблений цифровий пристрій необхідно перебрати всі можливі комбінації на інформаційних входах пристрою, та перевірити відповідність вихідних послідовностей до таблиці істинності(табл. 1.1).

TEST «SCHEME»

PERIOD: 100 нс;

INPUT С,R,D,А1,А2,В1,В2,В4;

OUTPUT С1,С2,С4,С8,С16;

C = (1:1,0:1):17;

R = 1:0,5, 0:17;

D = 0;

А1 = (1:1,0:1):17;

А2 = (1:2,0:2):17;

В1 = (1:4,0:4):17;

В2 = (1:8,0:8):17;

В4 = (1:16,0:16):2;

С1 = U:17;

С2 = U:17;

С4 = U:17;

С8 = U:17;

С16 = U:17;

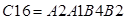

Часова діаграма роботи розробленого пристрою зображена на рисунку 5.1.

Набросок 5.1 – Часова діаграма тесту перевірки

Наведена часова діаграма роботи пристрою показує, що розроблений пристрій працює верно.

6. Розрахунок апаратних витрат

Кількість базових комірок для побудови загальної схеми розраховується за допомогою таблиці 6.1.

Таблиця 6.1 – Апаратні витрати

Назва елемента

Кількість елементів

Апаратні витрати на 1 елемент

Загальні апаратні витрати (БК)

V1W3

11

0,5

5,5

V1W2

4

1

4

V1

4

0,5

2

V2

5

0,5

2,5

V3

4

0,5

2

V4

1

0,5

0,5

V4V4

5

3,5

17,5

Всього

34

Розрахунок показує, що при хорошему розміщенні для реалізації лічильника на основі БМК 1515ХМ1 необхідно 34 базових комірок.

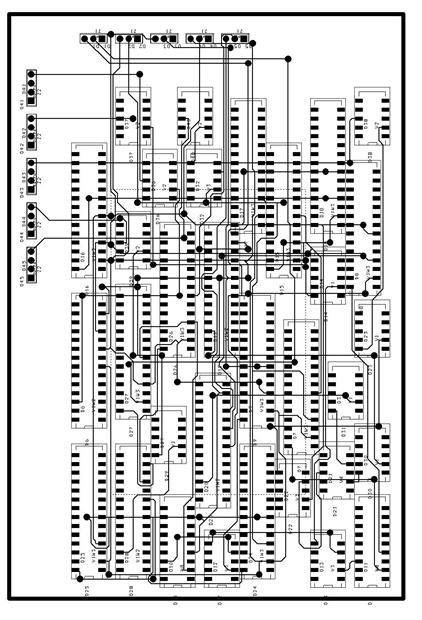

7. Розробка трафарету трасування

Итог розв’язку задачі трасування залежить не тільки від застосованого методу прокладки трас, а ще й від розв’язання низки пов’язаних між собою задач. Серед их можна виділити чотири базові задачі [1].

1. Складання списку з’єднань;

2. Розподіл з’єднань по шарах;

3. Визначення порядку трасування в дерматологическому шарі;

4. Проведення з’єднань або власне трасування.

Трасування БМК зводиться до нанесення електричних зв’язків між вибраними комірками з допомогою змінного шару металізації.Основою для виконання трасування є технологічне креслення-трафарет для розводки. Трафарет – це спрощене зображення базисного кристалу і додаткова інформація в умовному вигляді, на який накладається і з’єднується плівка для нанесення шарів розведення.Комірка типу VW складається з двох частин, розділених полікремнієвою шиною. Перша вміщує 4 транзистора, друга — 8. Комірка VN типу побудована на базі чотирьох транзисторів, тому її прив’язка відноситься до чотиритранзисторної частини комірки. Комірка WN типу побудована на базі восьми транзисторів, і місце її прив’язки визначається у восьмитранзисторній частині комірки.

Комірка VNWN має таку будову :

V — місце прив’язки комірки;

W — визначає, що комірка закінчується у восьмирозрядній частині комірки;

M — кількість полікремнієвих шин, які відділяють чотиритранзисторну частину комірки від восьмитранзисторної.

Якщо яка-небудь комірка не використовується, то на кресленні трасування залишаються порожні місця. В полі комутації можливе проведення провідників двох типів: полікремнієвих і алюмінієвих.

Горизонтальні лінії – це полікремнієві провідники, які покриті діелектрик-ним матеріалом, що дозволяє проводити над ними алюмінієві провідники. Контактні з’єднання з полікремнієвими провідниками можливі лише в спеціально відведених місцях (контактні площадки – вузли сітки). При виконанні креслень полікремнієві шини виконуються червоним кольором, алюмінієві провідники – чорним, а вертикальні лінії – зеленим кольором[5-6].

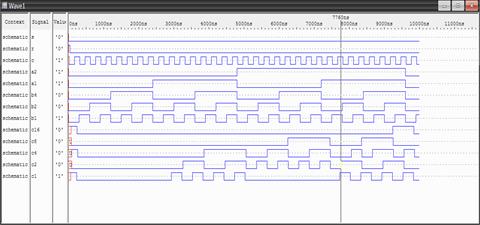

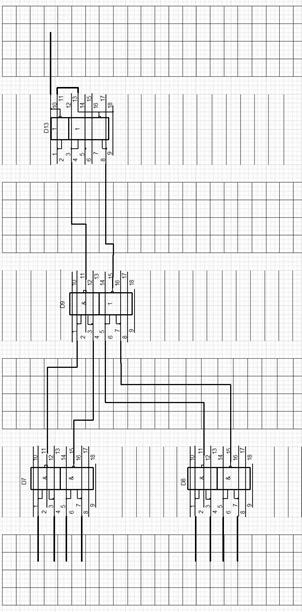

Для ручного трасування було взято фрагмент схеми, наведений на рис. 7.1.

Набросок 7.1 – Фрагмент схеми для ручного трасування

Трафарети автоматичного та ручного трасування наведені в додатках.

Висновки

При виконанні курсової роботи була розроблена велика інтегральна схема пристрою множення, який умножать 3-розрядне число на 2-розрядне на основі БМК 1515ХМ1. При синтезі використовувались базові бібліотечні елементи серії 1515ХМ1.

Багатоваріантний аналіз розв’язків поставленої задачі показав, що, для забезпечення оптимальної роботи пристрою, його потрібно робити комбінаційним. Розроблено принципову електричну схему та її логічну модель відповідно до поставлених вимог. Складено тест перевірки, який показав, що розроблений пристрій працює верно. Розраховано швидкодію(найбільша затримка становить 95,9 нс) та апаратні витрати(34 базових комірок) для реалізаці. Виконано автоматичне та ручне трасування схеми пристрою. Схема електрична принципова була розроблена, промодельована та протрасована в середовищі OrCAD 9.1.

Перечень використан

ої літератури

1. Методичні вказівки до проектування цифрових пристроїв на основі базових матричних кристалів для студентів спеціальності 2204 усіх форм навчання. /Сост. О.Н. Романюк — Вінниця: ВПИ, 1992./ — 36 с.

2. Майоров С.А., Новиков Г.И. структура электрических вычислительных машин. – Л.: Машиностроение. Ленинград. отд-ние, 1979. – 384с.

3. Применение интегральных микросхем в электрической вычислительной технике: Справочник / Р.В. Данилов, С.А. Ельцова, Ю.П. Иванов; Под ред. Б.Н. Файзулаева, Б.В. Тарабрина. – М.: Радио и связь, 1986. – 386с.

4. Справочник по интегральным микросхемам / Б.В.Тарабрин и др.; Под ред. Б.В. Тарабрина. — М.: Энергия, 1985.

5. Цифровые интегральные микросхемы: Справочник / М.И.Богданович и др.- Мн.: Беларусь: Полымя, 1996.

6. Корнейчук В.И. и др. Вычислительные устройства на микросхемах: Справочник. — К.: Техніка, 1986.

Додаток А

Міністерство освіти і науки України

Вінницький національний технічний університет

Інститут інформаційних технологій і компьютер’ютерної інженерії

Затверджую

Керівник, проф., д.т.н.

_________О.Н. Романюк

(підпис)

”___” _________ 200_ р.

ТЕХНІЧНЕ ЗАВДАННЯ

Розробити в базисі елементів БМК 1515ХМ1 велику інтегральну схему пристрою множення, який умножать 3-розрядне число на 2-розрядне.

1. Галузь застосування – пристрої обчислювальної техніки.

2. база розробки – робочий навчальний план дисципліни.

3. Мета та експлуатаційне призначення:

а) мета – отримання практичних навичок з автоматизованого проектування ВІС на основі БМК;

б) призначення розробки – навчальна курсова бота з дисципліни „САПР ЗОТ ”.

4. Джерела розробки – індивідуальне завдання на курсову боту з дисципліни та інші технічні матеріали до розрахунків та розробки схем.

5. Технічні вимоги

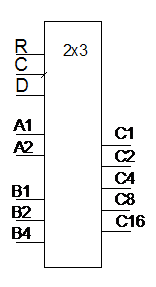

Функціональне позначення пристрою наведено на рисунку A.1.

Набросок A.1 – Функціональне позначення схеми пристрою

Розроблювальний пристрій містить такі заходи та виходи:

С – вхід, який використовується для переключення тригерів відповідно до вхідних сигналів;

D – технічний вхід, на який подається 0.

R – виконує функцію скидування тригерів в 0.

А1, А2 – інформаційні заходи, що задають 2-розрядне число;

В1, В2, В4 – інформаційні заходи, що задають 3-розрядне число;

С1, С2, С4, С8, С16 – інформаційні виходи, що визначають вихідне число.

6. Технічні свойства:

Кількість базових комірок не більше 50 шт, швидкодія не більше 100 нс..

7. Кліматичні умови

Забезпечити стабільну боту пристрою за мозгов його експлуатації в температурному діапазоні +5ºС…+40ºС і відносній вологості повітря не більше 75% та тиску – 720-740мм. рт. ст..

8. Конструктивні вимоги

Пристрій виконується у вигляді ВІС в базисі елементів БМК 1515 ХМ1.

9. Термін служби пристрою, рік – 100.

10. Показник безвідмовності, рік – 10.

11. Вимоги до рівня уніфікації та стандартизації

При розробці пристрою слід очень використовувати стандартні і уніфіковані деталі.

12. Графічна та текстова документація розробленого пристрою виновата відповідати діючим эталонам України

13. Стадії та етапи розробки пристою

Крайні терміни виконання КП – 7грудня 2009р.

Початок розробки – 26 вересня 2009 р.

14. порядок контролю та прийняття

Виконання етапів графічної та розрахункової документації курсової роботи контролюється викладачем згідно з графіком виконання проекту.

Прийняття курсової роботи здійснюється комісією, затвердженою зав. кафедрою згідно з графіком захисту.

Коректування технічного завдання допускається з дозволу керівника проекту.

Розробив студент гр. 1ПЗ-09сп _________________ Кравець В.В.

Додаток Б

СХЕМА ЕЛЕКТРИЧНА ПРИНЦИПОВА

Додаток В

ТРАФАРЕТ АВТОМАТИЧНОГО ТРАСУВАННЯ

Додаток Г

ТРАФАРЕТ РУЧНОГО ТРАСУВАННЯ

]]>